## КОНФЕРЕНЦИЯ FPGA РАЗРАБОТЧИКОВ

# FPGA-Systems 2021.1

Доступно в записи на Youtube

24 апреля 2021 года Москва, Сколково

# Бторая конференция FPGA разработчиков FPGA-Systems 2021.1

# Генерация HDL кода из моделей MATLAB/Simulink

Дмитрий Шидловский ЦИТМ Экспонента

# Характеристики разрабатываемой радиорелейной станции

| Скорость данных             | 2.048-155.520 Мбит/с                  |

|-----------------------------|---------------------------------------|

| Вид модуляции               | 64QAM, 32QAM, 16QAM, QPSK             |

| Кодирование                 | Duobinary Turbo Code (1/2, 3/4, 9/10) |

| Передискретизация/децимация | Фильтр Фарроу                         |

| Эквалайзер                  | LMS                                   |

| Синхронизация пакетов       | Согласованный фильтр                  |

| Формирование импульсов      | Приподнятый косинус                   |

| Аппаратная платформа        | ZYNQ-7 ZC706 и ADRV9371               |

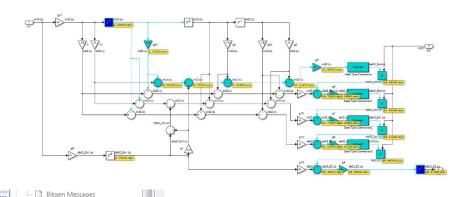

#### Построение системной модели

Эталон к которому обращались когда возникали проблемы с разработкой

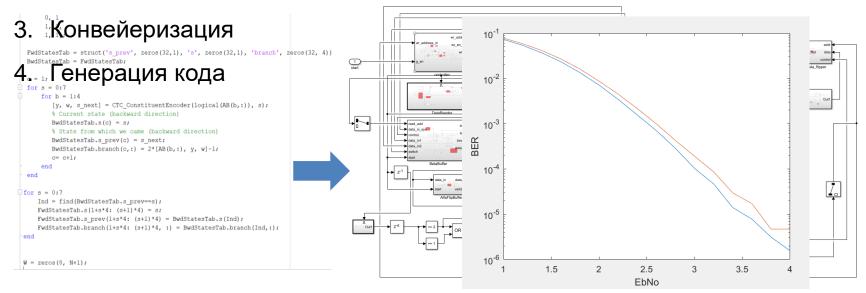

#### Реализация дубинарного турбо кодека

- 1. Трансформация структуры для эффективной реализации на аппаратуре

- 2. Перевод арифметики в фиксированную точку

### Отладка ошибок

Количество ошибок найденных с помощью различных методов отладки

| Отладка на модели                                                   | 85%  |  |

|---------------------------------------------------------------------|------|--|

| Отладка на модели с захваченными данными                            | 10%  |  |

| FIL тестирование                                                    | 2.5% |  |

| Отладка с использованием встроенного в ПЛИС логического анализатора | 2.5% |  |

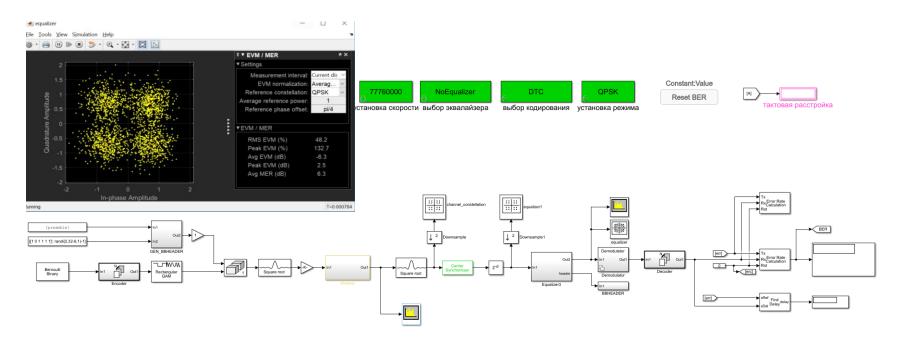

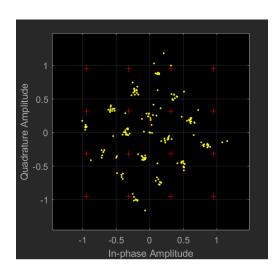

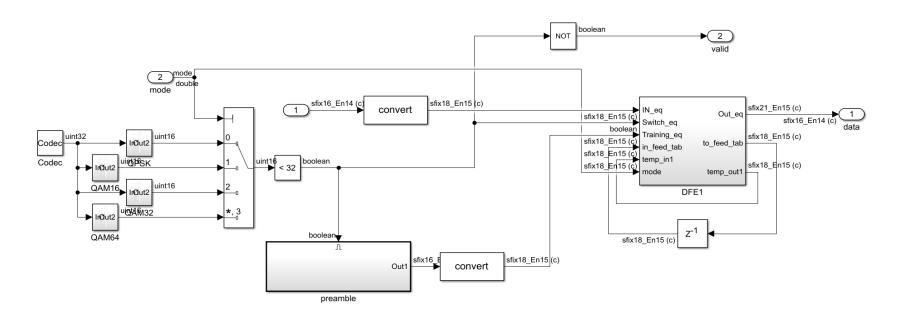

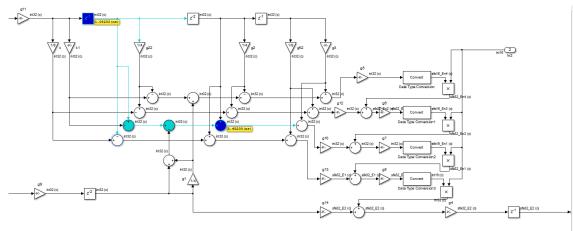

# Пример отладки на модели и на модели с захваченными данными

Реализация функции отключение эквалайзера

## Улучшение характеристик разрабатываемой системы

- Первый результат режима QPSK ¾ 9 дБ SNR для 1e-5

- Анализ бюджета выявил что наибольшую вклад вносит эквалайзер и канальный кодек на скорости ¾.

- Заменили эквалайзер с двумя отсчетами на выходной символ, на одно отсчетный на выходной символ, уменьшили шаг.

- Увеличили количество итераций кодека с 2 до 5

- Поменяли порядок выкалывания битов

- Текущий результат режима QPSK ¾ 7.2 дБ SNR для 1e-5

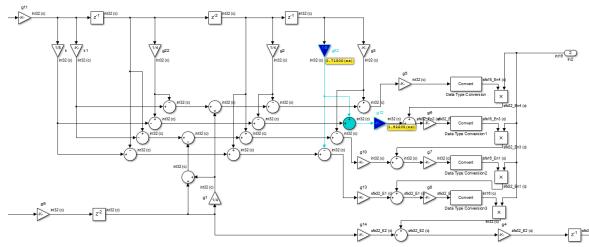

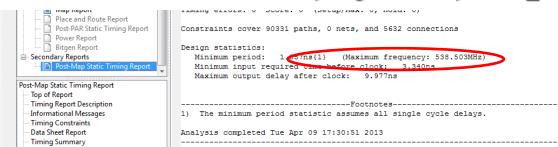

### Конвейеризация

Для обеспечения обработки отсчетов на частоте не менее 122.88 МГц

#### Оптимизация HDL кода

• Оптимизация на уровне алгоритма часто работает лучше, чем оптимизация через тонкие настройки синтезатора и разводчика

Дизайн с большим числом fanouts – разводится с таймингом -0.2 ns

```

%% write to buffer

if valIn

switch nIn

case 30

writeInd30 = fi(writeStart+(0:29),0,6,0,hdlfimath);

buffer(writeInd30+1) = dataIn((1:30)+2);

otherwise % case 32

writeInd32 = fi(writeStart+(0:31),0,6,0,hdlfimath);

buffer(writeInd32+1) = dataIn(1:32);

end

writeStart(:) = writeStart + nIn;

curLength(:) = curLength + nIn;

end

```

66 строк кода

Дизайн с меньшим числом fanouts – разводится с положительным таймингом, на 50% меньше LUT

136 строк кода

#### Результаты тестирования

#### Тестирование с имитатором канала

Разрабатываемая радиорелейная станция отработала без ошибок при тестировании через имитатор канала при следующих параметрах канала:

- Замирания Райса

- Вектор амплитуд [-24 0 -9 -14 -19 -23] дБ

- Вектор задержек [0 23.1 30.8 38.5 44.2 50] нс

- Доплер 0.5 Гц

Совпало с результатами моделирования (также при задании тропосферного канала (большие задержки между лучами), система не заработала как модели, так и с имитатором канала)

#### Ключевые аспекты ускорившие разработку

- Библиотека готовых блоков и переиспользование блоков из других проектов

- Большой процент нахождения ошибок на моделях (~95%)

- Быстрое нахождение скрытых ошибок связанных с переполнениями

- Автоматическая конвейризация

- Сокращение итерации от изменения алгоритма к получению рабочей прошивки

### Статистика проекта

| Календарное время                              | ~ 10 мес. |  |

|------------------------------------------------|-----------|--|

| Фактическое время                              | ~4-5 мес. |  |

| Время разработки первого прототипа             | ~3 мес.   |  |

| Время оптимизации системы                      | ~1 mec.   |  |

| Время тестирования с измерительной аппаратурой | ~1 mec.   |  |

| Строк VHDL кода                                | ~250 000  |  |

### Оценка качества сгенерированного кода

|                     | Post Route<br>Timing | Slice<br>Registers | Slice LUTs | LUT-FF | DSP48 | BUFG |  |  |

|---------------------|----------------------|--------------------|------------|--------|-------|------|--|--|

| DC OFFSET           |                      |                    |            |        |       |      |  |  |

| Generated code      | 506 MHz              | 319                | 329        | 400    | 0     | 1    |  |  |

| Hand-written code   | 400 MHz              | 738                | 680        | 790    | 0     | 0    |  |  |

| QDC                 |                      |                    |            |        |       |      |  |  |

| Generated code      | 311 MHz              | 873                | 633        | 712    | 20    | 1    |  |  |

| Hand-written code   | 417 MHz              | 1,446              | 1,008      | 1,177  | 15    | 1    |  |  |

| DDS                 |                      |                    |            |        |       |      |  |  |

| Generated code      | 391 MHz              | 211                | 148        | 213    | 0     | 1    |  |  |

| Hand-written code   | 445 MHz              | 222                | 204        | 224    | 0     | 1    |  |  |

| FARROW INTERPOLATOR |                      |                    |            |        |       |      |  |  |

| Generated code      | 286 MHz              | 1,112              | 1,077      | 1,180  | 10    | 1    |  |  |

| Hand-written code   | 375 MHz              | 3,664              | 3,900      | 4,017  | 10    | 1    |  |  |

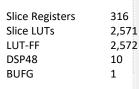

### Первая итерация

Timing summary: Timing errors: 0 Score: 0 (Setup/Max: 0, Hold: 0) Constraints cover 51190962820071856000000000000 paths, 0 nets, and 9716 connections Design statistics: Minimum period: 36.905ns{1} (Maximum frequency: 27.097MHz) Minimum input required time before clock: 39.109ns Maximum output delay after clock: 9.648ns -----Footnotes-----1) The minimum period statistic assumes all single cycle delays.

### Оптимизация операций с фиксированной точкой

Slice Registers

475

Slice LUTs

768

LUT-FF

778

DSP48

10

BUFG

1

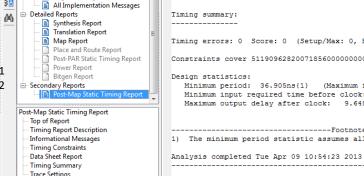

### Конвейеризация

Slice Registers

1,914

Slice LUTs

1,375

LUT-FF

1,536

DSP48

10

BUFG

1

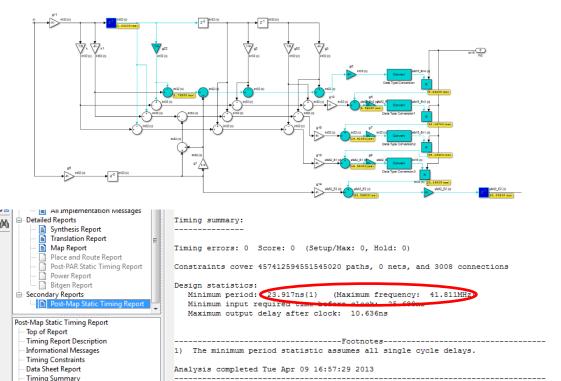

#### Оптимальный результат

Slice Register

1,112

Slice LUTs

1,077

LUT-FF

1,180

DSP48

10

BUFG

1

Constraints cover 113685 paths, 0 nets, and 4323 connections

Design statistics:

Minimum period: 3.487ns{1} (Maximum frequency: 286.779MHz)

Minimum input required time below the continuous output delay after clock: 9.496ns

The minimum period statistic assumes all single cycle delays.

Analysis completed Tue Apr 09 18:05:56 2013

### IP ядра

Цифровая обработка сигналов

Референс дизайн

Беспроводная связь

Системы LTE

Системы 5G

Нейросети

Компьютерное зрение

Кодирование

Цифровые Интерфейсы

Генерация кода для встраиваемых систем

https://exponenta.ru/news/ip-yadra-dlya-plis

## Где нас найти?

fpga-systems.ru

t.me/fpgasystems

youtube.com/c/fpgasystems

github.com/FPGA-Systems

vk.com/club185679360

admin@fpga-systems.ru

Генеральный партнёр конференции FPGA-Systems 2021.1

Первая современная отечественная САПР, реализующая сквозной цикл проектирования печатных плат

#### Более 30 вендоров уже присоединились для поддержки дизайн-центров

#### Инструменты поддержки для стартапов по электронике – «от идеи до рынка»

- https://SKOLKOVO.TOOLS аренда САПР по спец цене, изготовление MPW & miniASIC, IP-блоки

- Микрогранты: финансирование САПР, MPW, IP-блоков

- Менторская и консультационная поддержка

- Акселерация организация взаимодействия с крупными компаниями

#### Информационные партнёры

Сообщество приборостроителей

## Где нас найти?

fpga-systems.ru

t.me/fpgasystems

youtube.com/c/fpgasystems

github.com/FPGA-Systems

vk.com/club185679360

admin@fpga-systems.ru